# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corporation product best suited to the customer's application; they do not convey any

license under any intellectual property rights, or any other rights, belonging to Renesas Technology

Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

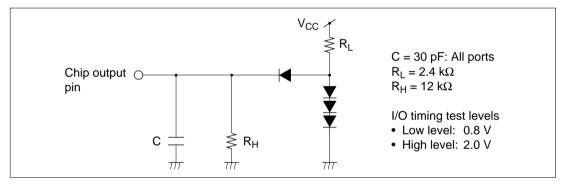

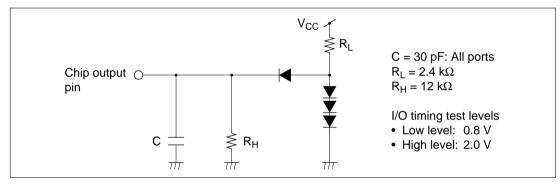

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# Hitachi 16-Bit Single-Chip Microcomputer

# H8S/2128 Series, H8S/2124 Series H8S/2128F-ZTAT<sup>TM</sup>

Hardware Manual — Supplement —

ADE-602-114B Rev. 3.0 5/22/02 Hitachi, Ltd.

#### Cautions

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party's

rights, including intellectual property rights, in connection with use of the information

contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# Announcement of Changes to Hardware Manual Contents

This is to announce that, with the addition of H8S/2128S and H8S/2127S products, a Supplement has been prepared for the following sections of the Hitachi single-chip microcomputer H8S/2128 Series and H8S/2124 Series Hardware Manual.

## Applicable Manual:

H8S/2128 Series, H8S/2124 Series, H8S/2128F-ZTAT Hardware Manual, 2nd Edition (ADE-602-114A), published September 1999

#### Applicable Sections:

Section 16, I<sup>2</sup>C Bus Interface → Replaced with "Supplement, Section 16" Sections 22–23, Electrical Characteristics → Replaced with "Supplement, Section 22" Appendix F, Product Code Lineup → Replaced with "Supplement, Appendix F"

Semiconductor & Integrated Circuits Hitachi, Ltd.

# Contents

| Secti | on 16    | I <sup>2</sup> C Bus Interface [Option]                | 1  |

|-------|----------|--------------------------------------------------------|----|

| 16.1  | Overvio  | ew                                                     | 1  |

|       | 16.1.1   | Features                                               | 1  |

|       | 16.1.2   | Block Diagram                                          | 2  |

|       | 16.1.3   | Input/Output Pins                                      | 4  |

|       |          | Register Configuration                                 | 5  |

| 16.2  | Registe  | r Descriptions                                         | 6  |

|       | 16.2.1   | I <sup>2</sup> C Bus Data Register (ICDR)              | 6  |

|       | 16.2.2   | Slave Address Register (SAR)                           | 9  |

|       | 16.2.3   | Second Slave Address Register (SARX)                   | 10 |

|       | 16.2.4   | I <sup>2</sup> C Bus Mode Register (ICMR)              | 11 |

|       | 16.2.5   | I <sup>2</sup> C Bus Control Register (ICCR)           | 14 |

|       | 16.2.6   | I <sup>2</sup> C Bus Status Register (ICSR)            | 21 |

|       |          | Serial/Timer Control Register (STCR)                   | 26 |

|       | 16.2.8   | DDC Switch Register (DDCSWR)                           | 27 |

|       |          | Module Stop Control Register (MSTPCR)                  | 29 |

| 16.3  |          | on                                                     | 30 |

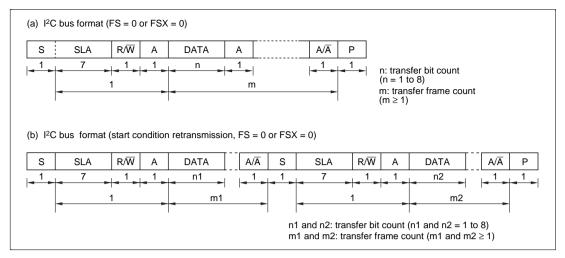

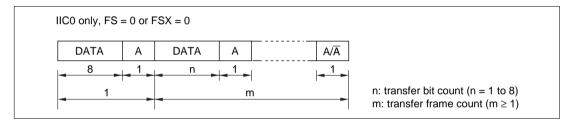

|       | -        | I <sup>2</sup> C Bus Data Format                       | 30 |

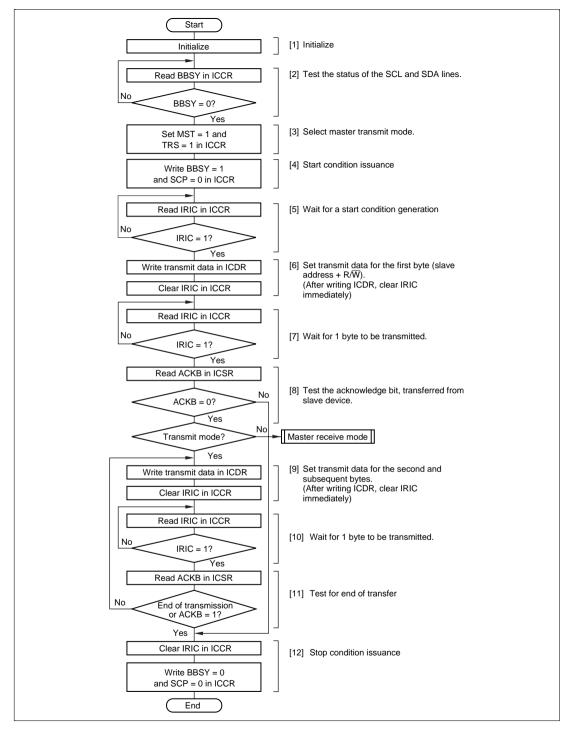

|       |          | Master Transmit Operation                              | 32 |

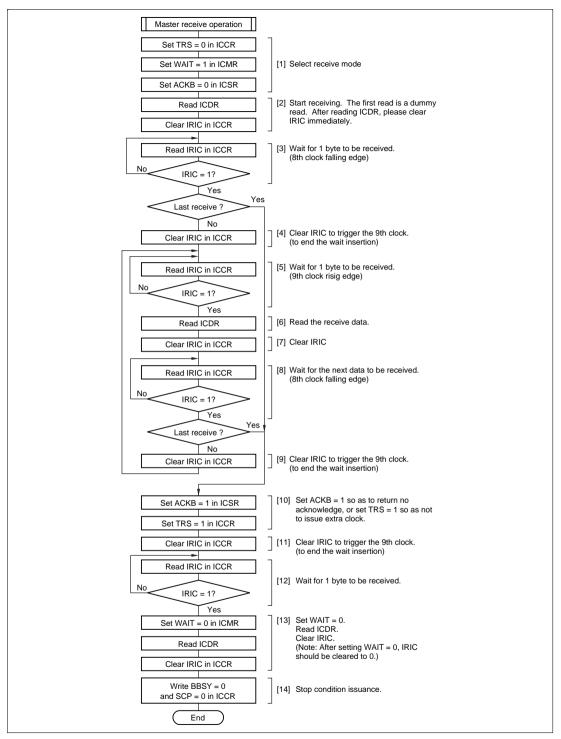

|       | 16.3.3   | Master Receive Operation                               | 34 |

|       | 16.3.4   | -                                                      | 37 |

|       | 16.3.5   | •                                                      | 39 |

|       | 16.3.6   | IRIC Setting Timing and SCL Control                    | 41 |

|       | 16.3.7   | 2                                                      | 42 |

|       | 16.3.8   | Operation Using the DTC                                | 43 |

|       |          | Noise Canceler                                         |    |

|       |          | Sample Flowcharts                                      |    |

|       |          | Initialization of Internal State                       | 48 |

| 16.4  |          | Notes                                                  | 50 |

|       | 8        |                                                        |    |

| Secti | on 22    | Electrical Characteristics                             | 57 |

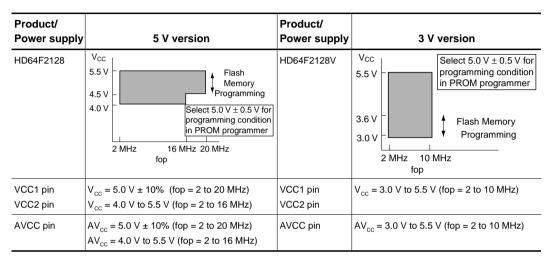

| 22.1  | Voltage  | e of Power Supply and Operating Range                  | 57 |

| 22.2  | Electric | cal Characteristics [H8S/2128 Series, H8S/2128 F-ZTAT] | 59 |

|       | 22.2.1   | Absolute Maximum Ratings                               | 59 |

|       | 22.2.2   | DC Characteristics                                     | 60 |

|       | 22.2.3   | AC Characteristics                                     | 71 |

|       | 22.2.4   | A/D Conversion Characteristics                         | 90 |

|       | 22.2.5   | Flash Memory Characteristics                           | 92 |

|       |          | Usage Note                                             |    |

|       |          |                                                        |    |

| 22.3 | Electric | cal Characteristics [H8S/2128S Series] | 95  |

|------|----------|----------------------------------------|-----|

|      |          | Absolute Maximum Ratings               |     |

|      | 22.3.2   | DC Characteristics                     | 96  |

|      | 22.3.3   | AC Characteristics                     | 107 |

|      | 22.3.4   | A/D Conversion Characteristics         | 126 |

|      | 22.3.5   | Usage Note                             | 128 |

| 22.4 | Electric | cal Characteristics [H8S/2124 Series]  | 130 |

|      |          | Absolute Maximum Ratings               |     |

|      | 22.4.2   | DC Characteristics                     | 131 |

|      | 22.4.3   | AC Characteristics                     | 138 |

|      |          | A/D Conversion Characteristics         |     |

|      | 22.4.5   | Usage Note                             | 157 |

| Appe | endix F  | Product Code Lineup                    | 159 |

# Section 16 I<sup>2</sup>C Bus Interface [Option]

A two-channel I<sup>2</sup>C bus interface is available as an option in the H8S/2128 Series. The I<sup>2</sup>C bus interface is not available for the H8S/2124 Series. Observe the following notes when using this option.

1. For mask-ROM versions, a W is added to the part number in products in which this optional function is used.

Examples: HD6432127SWFA

2. The product number is identical for F-ZTAT versions. However, be sure to inform your Hitachi sales representative if you will be using this option.

## 16.1 Overview

A two-channel  $I^2C$  bus interface is available for the H8S/2128 Series as an option. The  $I^2C$  bus interface conforms to and provides a subset of the Philips  $I^2C$  bus (inter-IC bus) interface functions. The register configuration that controls the  $I^2C$  bus differs partly from the Philips configuration, however.

Each I<sup>2</sup>C bus interface channel uses only one data line (SDA) and one clock line (SCL) to transfer data, saving board and connector space.

#### 16.1.1 Features

- Selection of addressing format or non-addressing format

- I<sup>2</sup>C bus format: addressing format with acknowledge bit, for master/slave operation

- Serial format: non-addressing format without acknowledge bit, for master operation only

- Conforms to Philips I<sup>2</sup>C bus interface (I<sup>2</sup>C bus format)

- Two ways of setting slave address (I<sup>2</sup>C bus format)

- Start and stop conditions generated automatically in master mode (I<sup>2</sup>C bus format)

- Selection of acknowledge output levels when receiving (I<sup>2</sup>C bus format)

- Automatic loading of acknowledge bit when transmitting (I<sup>2</sup>C bus format)

- Wait function in master mode (I<sup>2</sup>C bus format)

A wait can be inserted by driving the SCL pin low after data transfer, excluding acknowledgement. The wait can be cleared by clearing the interrupt flag.

- Wait function in slave mode (I<sup>2</sup>C bus format)

- A wait request can be generated by driving the SCL pin low after data transfer, excluding acknowledgement. The wait request is cleared when the next transfer becomes possible.

- Three interrupt sources

- Data transfer end (including transmission mode transition with I<sup>2</sup>C bus format and address reception after loss of master arbitration)

- Address match: when any slave address matches or the general call address is received in slave receive mode (I<sup>2</sup>C bus format)

- Stop condition detection

- Selection of 16 internal clocks (in master mode)

- Direct bus drive (with SCL and SDA pins)

- Two pins—P52/SCL0 and P47/SDA0—(normally NMOS push-pull outputs) function as NMOS open-drain outputs when the bus drive function is selected.

- Two pins—P24/SCL1 and P23/SDA1—(normally CMOS pins) function as NMOS-only outputs when the bus drive function is selected.

- Automatic switching from formatless mode to I<sup>2</sup>C bus format (channel 0 only)

- Slave mode addressless (no start condition/end condition, non-addressing) operation

- Operation using common data pin (SDA) and independent clock pin (VSYNCI, SCL) pin configuration

- Automatic switching from formatless mode to I<sup>2</sup>C bus format on fall of SCL

# 16.1.2 Block Diagram

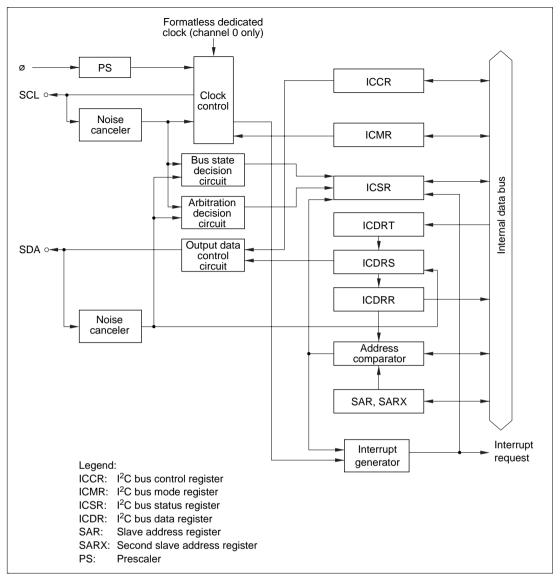

Figure 16.1 shows a block diagram of the I<sup>2</sup>C bus interface.

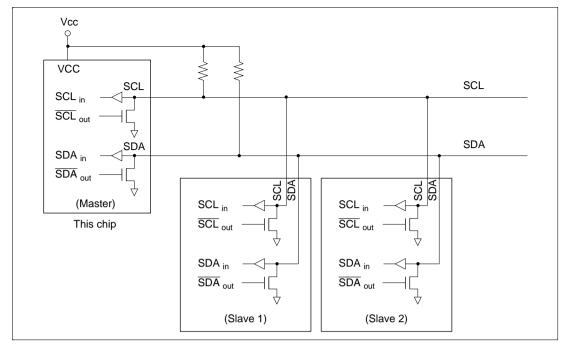

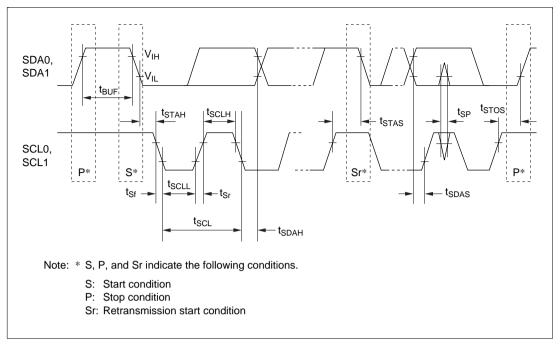

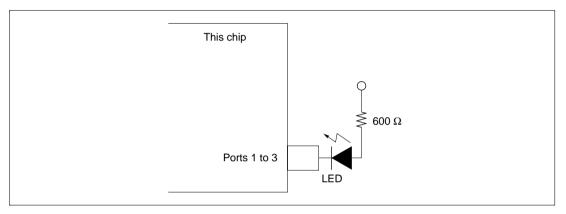

Figure 16.2 shows an example of I/O pin connections to external circuits. Channel 0 I/O pins and channel 1 I/O pins differ in structure, and have different specifications for permissible applied voltages. For details, see section 22, Electrical Characteristics.

Figure 16.1 Block Diagram of I<sup>2</sup>C Bus Interface

Figure 16.2 I<sup>2</sup>C Bus Interface Connections (Example: This Chip as Master)

## 16.1.3 Input/Output Pins

Table 16.1 summarizes the input/output pins used by the  $I^2C$  bus interface.

Table 16.1 I<sup>2</sup>C Bus Interface Pins

| Channel | Name                    | Abbreviation* | I/O   | Function                           |

|---------|-------------------------|---------------|-------|------------------------------------|

| 0       | Serial clock            | SCL0          | I/O   | IIC0 serial clock input/output     |

|         | Serial data             | SDA0          | I/O   | IIC0 serial data input/output      |

|         | Formatless serial clock | VSYNCI        | Input | IIC0 formatless serial clock input |

| 1       | Serial clock            | SCL1          | I/O   | IIC1 serial clock input/output     |

|         | Serial data             | SDA1          | I/O   | IIC1 serial data input/output      |

Note: \* In the text, the channel subscript is omitted, and only SCL and SDA are used.

# 16.1.4 Register Configuration

Table 16.2 summarizes the registers of the I<sup>2</sup>C bus interface.

**Table 16.2 Register Configuration**

| Channel | Name                                  | Abbreviation | R/W | Initial Value | Address*1 |

|---------|---------------------------------------|--------------|-----|---------------|-----------|

| 0       | I <sup>2</sup> C bus control register | ICCR0        | R/W | H'01          | H'FFD8    |

|         | I <sup>2</sup> C bus status register  | ICSR0        | R/W | H'00          | H'FFD9    |

|         | I <sup>2</sup> C bus data register    | ICDR0        | R/W | <del></del>   | H'FFDE*2  |

|         | I <sup>2</sup> C bus mode register    | ICMR0        | R/W | H'00          | H'FFDF*2  |

|         | Slave address register                | SAR0         | R/W | H'00          | H'FFDF*2  |

|         | Second slave address register         | SARX0        | R/W | H'01          | H'FFDE*2  |

| 1       | I <sup>2</sup> C bus control register | ICCR1        | R/W | H'01          | H'FF88    |

|         | I <sup>2</sup> C bus status register  | ICSR1        | R/W | H'00          | H'FF89    |

|         | I <sup>2</sup> C bus data register    | ICDR1        | R/W | <del></del>   | H'FF8E*2  |

|         | I <sup>2</sup> C bus mode register    | ICMR1        | R/W | H'00          | H'FF8F*2  |

|         | Slave address register                | SAR1         | R/W | H'00          | H'FF8F*2  |

|         | Second slave address register         | SARX1        | R/W | H'01          | H'FF8E*2  |

| Common  | Serial/timer control register         | STCR         | R/W | H'00          | H'FFC3    |

|         | DDC switch register                   | DDCSWR       | R/W | H'0F          | H'FEE6    |

|         | Module stop control register          | MSTPCRH      | R/W | H'3F          | H'FF86    |

|         |                                       | MSTPCRL      | R/W | H'FF          | H'FF87    |

Notes: \*1 Lower 16 bits of the address.

The I<sup>2</sup>C bus interface registers are assigned to the same addresses as other registers. Register selection is performed by means of the IICE bit in the serial/timer control register (STCR).

<sup>\*2</sup> The register that can be written or read depends on the ICE bit in the I<sup>2</sup>C bus control register. The slave address register can be accessed when ICE = 0, and the I<sup>2</sup>C bus mode register can be accessed when ICE = 1.

# **16.2** Register Descriptions

# 16.2.1 I<sup>2</sup>C Bus Data Register (ICDR)

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

|               | ICDR7 | ICDR6 | ICDR5 | ICDR4 | ICDR3 | ICDR2 | ICDR1 | ICDR0 |

| Initial value | _     | _     | _     | _     | _     | _     | _     | _     |

| Read/Write    | R/W   |

# • ICDRR

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | ICDRR7 | ICDRR6 | ICDRR5 | ICDRR4 | ICDRR3 | ICDRR2 | ICDRR1 | ICDRR0 |

| Initial value | _      | _      | _      | _      | _      | _      | _      | _      |

| Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      |

## • ICDRS

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | ICDRS7 | ICDRS6 | ICDRR5 | ICDRS4 | ICDRS3 | ICDRS2 | ICDRS1 | ICDRS0 |

| Initial value | _      | _      | _      | _      | _      | _      | _      | _      |

| Read/Write    | _      | _      | _      | _      | _      | _      | _      | _      |

# ICDRT

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | ICDRT7 | ICDRT6 | ICDRT5 | ICDRT4 | ICDRT3 | ICDRT2 | ICDRT1 | ICDRT0 |

| Initial value | _      | _      | _      | _      | _      | _      | _      |        |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

# • TDRE, RDRF (internal flags)

| Bit           |      | _    |

|---------------|------|------|

|               | TDRE | RDRF |

| Initial value | 0    | 0    |

| Read/Write    | _    | _    |

ICDR is an 8-bit readable/writable register that is used as a transmit data register when transmitting and a receive data register when receiving. ICDR is divided internally into a shift register (ICDRS), receive buffer (ICDRR), and transmit buffer (ICDRT). ICDRS cannot be read or written by the CPU, ICDRR is read-only, and ICDRT is write-only. Data transfers among the three registers are performed automatically in coordination with changes in the bus state, and affect the status of internal flags such as TDRE and RDRF.

If IIC is in transmit mode and the next data is in ICDRT (the TDRE flag is 0) following transmission/reception of one frame of data using ICDRS, data is transferred automatically from ICDRT to ICDRS. If IIC is in receive mode and no previous data remains in ICDRR (the RDRF flag is 0) following transmission/reception of one frame of data using ICDRS, data is transferred automatically from ICDRS to ICDRR.

If the number of bits in a frame, excluding the acknowledge bit, is less than 8, transmit data and receive data are stored differently. Transmit data should be written justified toward the MSB side when MLS = 0, and toward the LSB side when MLS = 1. Receive data bits read from the LSB side should be treated as valid when MLS = 0, and bits read from the MSB side when MLS = 1.

ICDR is assigned to the same address as SARX, and can be written and read only when the ICE bit is set to 1 in ICCR.

The value of ICDR is undefined after a reset.

The TDRE and RDRF flags are set and cleared under the conditions shown below. Setting the TDRE and RDRF flags affects the status of the interrupt flags.

| TDRE | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 0    | The next transmit data is in ICDR (ICDRT), or transmission cannot be started (Initial value)                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|      | [Clearing conditions]                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|      | <ul> <li>When transmit data is written in ICDR (ICDRT) in transmit mode (TRS = 1)</li> <li>When a stop condition is detected in the bus line state after a stop condition is issued with the I²C bus format or serial format selected</li> <li>When a stop condition is detected with the I²C bus format selected</li> <li>In receive mode (TRS = 0) <ul> <li>(A 0 write to TRS during transfer is valid after reception of a frame containing an acknowledge bit)</li> </ul> </li> </ul> |  |  |  |  |  |  |  |  |

| 1    | The next transmit data can be written in ICDR (ICDRT)                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|      | [Setting conditions]                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|      | <ul> <li>In transmit mode (TRS = 1), when a start condition is detected in the bus line state after a start condition is issued in master mode with the I<sup>2</sup>C bus format or serial format selected</li> </ul>                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|      | <ul> <li>At the first transmit mode setting (TRS = 1) (first transmit mode setting only) after<br/>the mode is switched from I<sup>2</sup>C bus mode to formatless mode</li> </ul>                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|      | When data is transferred from ICDRT to ICDRS                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|      | (Data transfer from ICDRT to ICDRS when TRS = 1 and TDRE = 0, and ICDRS is empty)                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| RDRF | Description                                                                   |                 |  |  |  |  |  |

|------|-------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| 0    | The data in ICDR (ICDRR) is invalid                                           | (Initial value) |  |  |  |  |  |

|      | [Clearing condition]                                                          |                 |  |  |  |  |  |

|      | When ICDR (ICDRR) receive data is read in receive mode                        |                 |  |  |  |  |  |

| 1    | The ICDR (ICDRR) receive data can be read                                     |                 |  |  |  |  |  |

|      | [Setting condition]                                                           |                 |  |  |  |  |  |

|      | When data is transferred from ICDRS to ICDRR                                  |                 |  |  |  |  |  |

|      | (Data transfer from ICDRS to ICDRR in case of normal termination wi RDRF = 0) | th TRS = 0 and  |  |  |  |  |  |

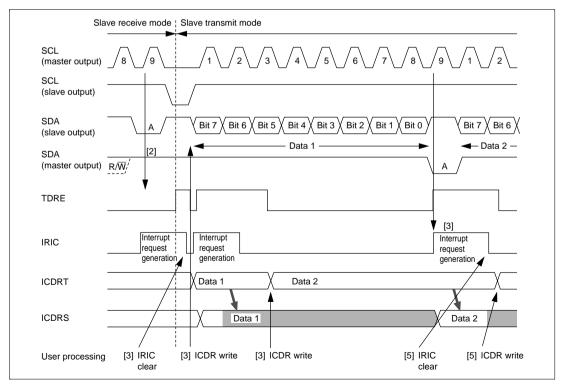

When detecting a start condition and then switching from slave receive mode (TRS = 0) state to transmit mode (TRS = 1) (first transmit mode switching only).

#### 16.2.2 Slave Address Register (SAR)

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0   |

|---------------|------|------|------|------|------|------|------|-----|

|               | SVA6 | SVA5 | SVA4 | SVA3 | SVA2 | SVA1 | SVA0 | FS  |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   |

| Read/Write    | R/W  | R/W |

SAR is an 8-bit readable/writable register that stores the slave address and selects the communication format. When the chip is in slave mode (and the addressing format is selected), if the upper 7 bits of SAR match the upper 7 bits of the first frame received after a start condition, the chip operates as the slave device specified by the master device. SAR is assigned to the same address as ICMR, and can be written and read only when the ICE bit is cleared to 0 in ICCR.

SAR is initialized to H'00 by a reset and in hardware standby mode.

**Bits 7 to 1—Slave Address (SVA6 to SVA0):** Set a unique address in bits SVA6 to SVA0, differing from the addresses of other slave devices connected to the I<sup>2</sup>C bus.

**Bit 0—Format Select (FS):** Used together with the FSX bit in SARX and the SW bit in DDCSWR to select the communication format.

- I<sup>2</sup>C bus format: addressing format with acknowledge bit

- Synchronous serial format: non-addressing format without acknowledge bit, for master mode only

- Formatless mode (channel 0 only): non-addressing format with or without acknowledge bit, slave mode only, start/stop conditions not detected

The FS bit also specifies whether or not SAR slave address recognition is performed in slave mode.

| Bit 6 | Bit 0 | Bit 0 |                                                             |

|-------|-------|-------|-------------------------------------------------------------|

| SW    | FS    | FSX   | Operating Mode                                              |

| 0     | 0     | 0     | I <sup>2</sup> C bus format                                 |

|       |       |       | <ul> <li>SAR and SARX slave addresses recognized</li> </ul> |

|       |       | 1     | I <sup>2</sup> C bus format (Initial value)                 |

|       |       |       | <ul> <li>SAR slave address recognized</li> </ul>            |

|       |       |       | SARX slave address ignored                                  |

|       | 1     | 0     | I <sup>2</sup> C bus format                                 |

|       |       |       | <ul> <li>SAR slave address ignored</li> </ul>               |

|       |       |       | <ul> <li>SARX slave address recognized</li> </ul>           |

|       |       | 1     | Synchronous serial format                                   |

|       |       |       | <ul> <li>SAR and SARX slave addresses ignored</li> </ul>    |

| 1     | 0     | 0     | Formatless mode (start/stop conditions not detected)        |

|       | 0     | 1     | Acknowledge bit used                                        |

|       | 1     | 0     |                                                             |

|       | 1     | 1     | Formatless mode* (start/stop conditions not detected)       |

|       |       |       | No acknowledge bit                                          |

Note: \* Do not set this mode when automatic switching to the I<sup>2</sup>C bus format is performed by means of the DDCSWR setting.

# 16.2.3 Second Slave Address Register (SARX)

CADV

DDCCWD CAD

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0   |

|---------------|-------|-------|-------|-------|-------|-------|-------|-----|

|               | SVAX6 | SVAX5 | SVAX4 | SVAX3 | SVAX2 | SVAX1 | SVAX0 | FSX |

| Initial value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1   |

| Read/Write    | R/W   | R/W |

SARX is an 8-bit readable/writable register that stores the second slave address and selects the communication format. When the chip is in slave mode (and the addressing format is selected), if the upper 7 bits of SARX match the upper 7 bits of the first frame received after a start condition, the chip operates as the slave device specified by the master device. SARX is assigned to the same address as ICDR, and can be written and read only when the ICE bit is cleared to 0 in ICCR.

SARX is initialized to H'01 by a reset and in hardware standby mode.

**Bits 7 to 1—Second Slave Address (SVAX6 to SVAX0):** Set a unique address in bits SVAX6 to SVAX0, differing from the addresses of other slave devices connected to the I<sup>2</sup>C bus.

**Bit 0—Format Select X (FSX):** Used together with the FS bit in SAR and the SW bit in DDCSWR to select the communication format.

- I<sup>2</sup>C bus format: addressing format with acknowledge bit

- Synchronous serial format: non-addressing format without acknowledge bit, for master mode only

- Formatless mode: non-addressing format with or without acknowledge bit, slave mode only, start/stop conditions not detected

The FSX bit also specifies whether or not SARX slave address recognition is performed in slave mode. For details, see the description of the FS bit in SAR.

### 16.2.4 I<sup>2</sup>C Bus Mode Register (ICMR)

| Bit           | 7   | 6    | 5    | 4    | 3    | 2   | 1   | 0   |

|---------------|-----|------|------|------|------|-----|-----|-----|

|               | MLS | WAIT | CKS2 | CKS1 | CKS0 | BC2 | BC1 | BC0 |

| Initial value | 0   | 0    | 0    | 0    | 0    | 0   | 0   | 0   |

| Read/Write    | R/W | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W |

ICMR is an 8-bit readable/writable register that selects whether the MSB or LSB is transferred first, performs master mode wait control, and selects the master mode transfer clock frequency and the transfer bit count. ICMR is assigned to the same address as SAR. ICMR can be written and read only when the ICE bit is set to 1 in ICCR.

ICMR is initialized to H'00 by a reset and in hardware standby mode.

**Bit 7—MSB-First/LSB-First Select (MLS):** Selects whether data is transferred MSB-first or LSB-first.

If the number of bits in a frame, excluding the acknowledge bit, is less than 8, transmit data and receive data are stored differently. Transmit data should be written justified toward the MSB side when MLS = 0, and toward the LSB side when MLS = 1. Receive data bits read from the LSB side should be treated as valid when MLS = 0, and bits read from the MSB side when MLS = 1.

Do not set this bit to 1 when the I<sup>2</sup>C bus format is used.

Bit 7

| MLS | Description |                 |

|-----|-------------|-----------------|

| 0   | MSB-first   | (Initial value) |

| 1   | LSB-first   |                 |

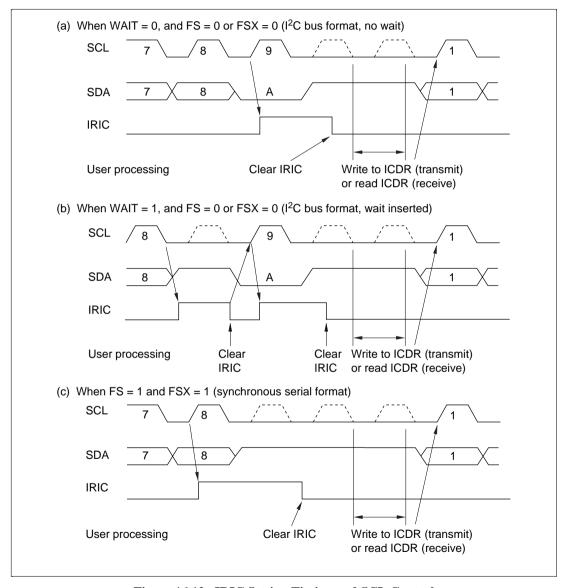

**Bit 6—Wait Insertion Bit (WAIT):** Selects whether to insert a wait between the transfer of data and the acknowledge bit, in master mode with the I<sup>2</sup>C bus format. When WAIT is set to 1, after the fall of the clock for the final data bit, the IRIC flag is set to 1 in ICCR, and a wait state begins (with SCL at the low level). When the IRIC flag is cleared to 0 in ICCR, the wait ends and the acknowledge bit is transferred. If WAIT is cleared to 0, data and acknowledge bits are transferred consecutively with no wait inserted.

The IRIC flag in ICCR is set to 1 on completion of the acknowledge bit transfer, regardless of the WAIT setting.

The setting of this bit is invalid in slave mode.

Bit 6

| WAIT | Description                                         |                 |

|------|-----------------------------------------------------|-----------------|

| 0    | Data and acknowledge bits transferred consecutively | (Initial value) |

| 1    | Wait inserted between data and acknowledge bits     |                 |

**Bits 5 to 3—Serial Clock Select (CKS2 to CKS0):** These bits, together with the IICX1 (channel 1) or IICX0 (channel 0) bit in the STCR register, select the serial clock frequency in master mode. They should be set according to the required transfer rate.

STCR Bit 5 or 6 Bit 5 Bit 4 Bit 3

| _ |    |   |   |   |     | _ |   |    |

|---|----|---|---|---|-----|---|---|----|

|   | ro | n | 0 | 2 | r I | • | 2 | te |

|   |    |   |   |   |     |   |   |    |

| IICX | CKS2 | CKS1 | CKS0 | Clock | ø =<br>5 MHz | ø =<br>8 MHz | ø =<br>10 MHz | ø =<br>16 MHz | ø =<br>20 MHz |

|------|------|------|------|-------|--------------|--------------|---------------|---------------|---------------|

| 0    | 0    | 0    | 0    | ø/28  | 179 kHz      | 286 kHz      | 357 kHz       | 571 kHz*      | 714 kHz*      |

|      |      |      | 1    | ø/40  | 125 kHz      | 200 kHz      | 250 kHz       | 400 kHz       | 500 kHz*      |

|      |      | 1    | 0    | ø/48  | 104 kHz      | 167 kHz      | 208 kHz       | 333 kHz       | 417 kHz*      |

|      |      |      | 1    | ø/64  | 78.1 kHz     | 125 kHz      | 156 kHz       | 250 kHz       | 313 kHz       |

|      | 1    | 0    | 0    | ø/80  | 62.5 kHz     | 100 kHz      | 125 kHz       | 200 kHz       | 250 kHz       |

|      |      |      | 1    | ø/100 | 50.0 kHz     | 80.0 kHz     | 100 kHz       | 160 kHz       | 200 kHz       |

|      |      | 1    | 0    | ø/112 | 44.6 kHz     | 71.4 kHz     | 89.3 kHz      | 143 kHz       | 179 kHz       |

|      |      |      | 1    | ø/128 | 39.1 kHz     | 62.5 kHz     | 78.1 kHz      | 125 kHz       | 156 kHz       |

| 1    | 0    | 0    | 0    | ø/56  | 89.3 kHz     | 143 kHz      | 179 kHz       | 286 kHz       | 357 kHz       |

|      |      |      | 1    | ø/80  | 62.5 kHz     | 100 kHz      | 125 kHz       | 200 kHz       | 250 kHz       |

|      |      | 1    | 0    | ø/96  | 52.1 kHz     | 83.3 kHz     | 104 kHz       | 167 kHz       | 208 kHz       |

|      |      |      | 1    | ø/128 | 39.1 kHz     | 62.5 kHz     | 78.1 kHz      | 125 kHz       | 156 kHz       |

|      | 1    | 0    | 0    | ø/160 | 31.3 kHz     | 50.0 kHz     | 62.5 kHz      | 100 kHz       | 125 kHz       |

|      |      |      | 1    | ø/200 | 25.0 kHz     | 40.0 kHz     | 50.0 kHz      | 80.0 kHz      | 100 kHz       |

|      |      | 1    | 0    | ø/224 | 22.3 kHz     | 35.7 kHz     | 44.6 kHz      | 71.4 kHz      | 89.3 kHz      |

|      |      |      | 1    | ø/256 | 19.5 kHz     | 31.3 kHz     | 39.1 kHz      | 62.5 kHz      | 78.1 kHz      |

Note: \* Outside the I<sup>2</sup>C bus interface specification range (normal mode: max. 100 kHz; high-speed mode: max. 400 kHz).

**Bits 2 to 0—Bit Counter (BC2 to BC0):** Bits BC2 to BC0 specify the number of bits to be transferred next. With the I<sup>2</sup>C bus format (when the FS bit in SAR or the FSX bit in SARX is 0), the data is transferred with one addition acknowledge bit. Bit BC2 to BC0 settings should be made during an interval between transfer frames. If bits BC2 to BC0 are set to a value other than 000, the setting should be made while the SCL line is low.

The bit counter is initialized to 000 by a reset and when a start condition is detected. The value returns to 000 at the end of a data transfer, including the acknowledge bit.

| Bit 2 | Bit 1 | Bit 0 | Bits                      | /Frame                      |                 |

|-------|-------|-------|---------------------------|-----------------------------|-----------------|

| BC2   | BC1   | BC0   | Synchronous Serial Format | I <sup>2</sup> C Bus Format |                 |

| 0     | 0     | 0     | 8                         | 9                           | (Initial value) |

|       |       | 1     | 1                         | 2                           |                 |

|       | 1     | 0     | 2                         | 3                           |                 |

|       |       | 1     | 3                         | 4                           |                 |

| 1     | 0     | 0     | 4                         | 5                           |                 |

|       |       | 1     | 5                         | 6                           |                 |

|       | 1     | 0     | 6                         | 7                           |                 |

|       |       | 1     | 7                         | 8                           |                 |

# 16.2.5 I<sup>2</sup>C Bus Control Register (ICCR)

| Bit           | 7   | 6    | 5   | 4   | 3    | 2    | 1      | 0   |

|---------------|-----|------|-----|-----|------|------|--------|-----|

|               | ICE | IEIC | MST | TRS | ACKE | BBSY | IRIC   | SCP |

| Initial value | 0   | 0    | 0   | 0   | 0    | 0    | 0      | 1   |

| Read/Write    | R/W | R/W  | R/W | R/W | R/W  | R/W  | R/(W)* | W   |

Note: \* Only 0 can be written, to clear the flag.

ICCR is an 8-bit readable/writable register that enables or disables the I<sup>2</sup>C bus interface, enables or disables interrupts, selects master or slave mode and transmission or reception, enables or disables acknowledgement, confirms the I<sup>2</sup>C bus interface bus status, issues start/stop conditions, and performs interrupt flag confirmation.

ICCR is initialized to H'01 by a reset and in hardware standby mode.

Bit 7—I<sup>2</sup>C Bus Interface Enable (ICE): Selects whether or not the I<sup>2</sup>C bus interface is to be used. When ICE is set to 1, port pins function as SCL and SDA input/output pins and transfer operations are enabled. When ICE is cleared to 0, the I<sup>2</sup>C bus interface module is halted and its internal states are cleared.

The SAR and SARX registers can be accessed when ICE is 0. The ICMR and ICDR registers can be accessed when ICE is 1.

Bit 7

| ICE | Description                                                                                       |                     |

|-----|---------------------------------------------------------------------------------------------------|---------------------|

| 0   | I <sup>2</sup> C bus interface module disabled, with SCL and SDA signal pins set to port function | (Initial value)     |

|     | I <sup>2</sup> C bus interface module internal states initialized                                 |                     |

|     | SAR and SARX can be accessed                                                                      |                     |

| 1   | I <sup>2</sup> C bus interface module enabled for transfer operations (pins SCL the bus)          | and SCA are driving |

|     | ICMR and ICDR can be accessed                                                                     |                     |

Bit 6—I<sup>2</sup>C Bus Interface Interrupt Enable (IEIC): Enables or disables interrupts from the I<sup>2</sup>C bus interface to the CPU.

#### Bit 6

| IEIC | Description         |                 |

|------|---------------------|-----------------|

| 0    | Interrupts disabled | (Initial value) |

| 1    | Interrupts enabled  |                 |

#### Bit 5—Master/Slave Select (MST)

#### Bit 4—Transmit/Receive Select (TRS)

MST selects whether the I<sup>2</sup>C bus interface operates in master mode or slave mode.

TRS selects whether the I<sup>2</sup>C bus interface operates in transmit mode or receive mode.

In master mode with the  $I^2C$  bus format, when arbitration is lost, MST and TRS are both reset by hardware, causing a transition to slave receive mode. In slave receive mode with the addressing format (FS = 0 or FSX = 0), hardware automatically selects transmit or receive mode according to the  $R/\overline{W}$  bit in the first frame after a start condition.

Modification of the TRS bit during transfer is deferred until transfer of the frame containing the acknowledge bit is completed, and the changeover is made after completion of the transfer.

MST and TRS select the operating mode as follows.

| Bit 5 | Bit 4 |                      |                 |

|-------|-------|----------------------|-----------------|

| MST   | TRS   | Operating Mode       |                 |

| 0     | 0     | Slave receive mode   | (Initial value) |

|       | 1     | Slave transmit mode  |                 |

| 1     | 0     | Master receive mode  |                 |

|       | 1     | Master transmit mode |                 |

# Bit 5

| MST | Description                                                                                                                 |              |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|

| 0   | Slave mode (In                                                                                                              |              |  |  |  |  |  |

|     | [Clearing conditions]                                                                                                       |              |  |  |  |  |  |

|     | 1. When 0 is written by software                                                                                            |              |  |  |  |  |  |

|     | <ol> <li>When bus arbitration is lost after transmission is started in I<sup>2</sup>C bus<br/>format master mode</li> </ol> |              |  |  |  |  |  |

| 1   | Master mode                                                                                                                 |              |  |  |  |  |  |

|     | [Setting conditions]                                                                                                        |              |  |  |  |  |  |

|     | 1. When 1 is written by software (in cases other than clearing condition 2)                                                 |              |  |  |  |  |  |

|     | 2. When 1 is written in MST after reading MST = 0 (in case of clearing                                                      | condition 2) |  |  |  |  |  |

# Bit 4

| TRS | Description                                                                                                                 |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0   | Receive mode (Initial value)                                                                                                |  |  |  |  |  |  |

|     | [Clearing conditions]                                                                                                       |  |  |  |  |  |  |

|     | <ol> <li>When 0 is written by software (in cases other than setting condition</li> <li>3)</li> </ol>                        |  |  |  |  |  |  |

|     | <ol><li>When 0 is written in TRS after reading TRS = 1 (in case of clearing<br/>condition 3)</li></ol>                      |  |  |  |  |  |  |

|     | <ol> <li>When bus arbitration is lost after transmission is started in I<sup>2</sup>C bus<br/>format master mode</li> </ol> |  |  |  |  |  |  |

|     | 4. When the SW bit in DDCSWR changes from 1 to 0                                                                            |  |  |  |  |  |  |

| 1   | Transmit mode                                                                                                               |  |  |  |  |  |  |

|     | [Setting conditions]                                                                                                        |  |  |  |  |  |  |

|     | 1. When 1 is written by software (in cases other than clearing conditions 3 and 4)                                          |  |  |  |  |  |  |

|     | <ol><li>When 1 is written in TRS after reading TRS = 0 (in case of clearing conditions 3 and 4)</li></ol>                   |  |  |  |  |  |  |

|     | 3. When a 1 is received as the $R/\overline{W}$ bit of the first frame in $I^2C$ bus format slave mode                      |  |  |  |  |  |  |

**Bit 3—Acknowledge Bit Judgement Selection (ACKE):** Specifies whether the value of the acknowledge bit returned from the receiving device when using the I<sup>2</sup>C bus format is to be ignored and continuous transfer is performed, or transfer is to be aborted and error handling, etc., performed if the acknowledge bit is 1. When the ACKE bit is 0, the value of the received acknowledge bit is not indicated by the ACKB bit, which is always 0.

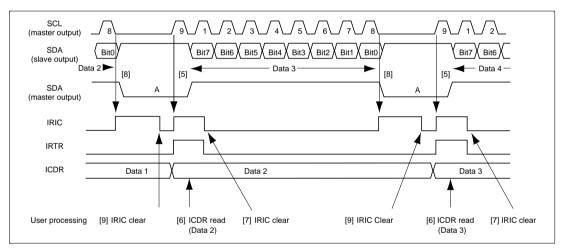

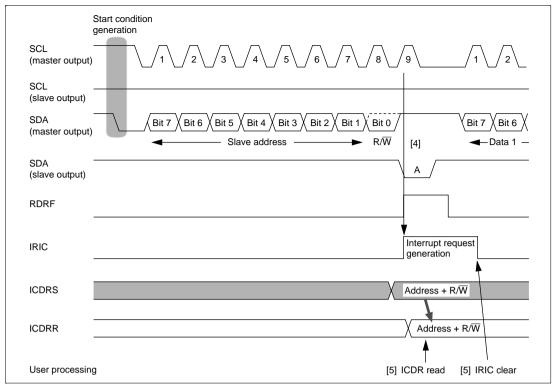

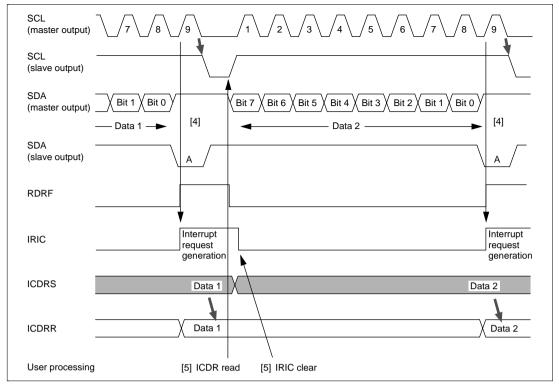

In the H8S/2128 Series, the DTC can be used to perform continuous transfer. The DTC is activated when the IRTR interrupt flag is set to 1 (IRTR is one of two interrupt flags, the other being IRIC). When the ACKE bit is 0, the TDRE, IRIC, and IRTR flags are set on completion of data transmission, regardless of the value of the acknowledge bit. When the ACKE bit is 1, the TDRE, IRIC, and IRTR flags are set on completion of data transmission when the acknowledge bit is 0, and the IRIC flag alone is set on completion of data transmission when the acknowledge bit is 1.

When the DTC is activated, the TDRE, IRIC, and IRTR flags are cleared to 0 after the specified number of data transfers have been executed. Consequently, interrupts are not generated during continuous data transfer, but if data transmission is completed with a 1 acknowledge bit when the ACKE bit is set to 1, the DTC is not activated and an interrupt is generated, if enabled.

Depending on the receiving device, the acknowledge bit may be significant, in indicating completion of processing of the received data, for instance, or may be fixed at 1 and have no significance.

#### Bit 3

| ACKE | <br>Description                                                                   |                 |

|------|-----------------------------------------------------------------------------------|-----------------|

| 0    | The value of the acknowledge bit is ignored, and continuous transfer is performed | (Initial value) |

| 1    | If the acknowledge bit is 1, continuous transfer is interrupted                   |                 |

**Bit 2—Bus Busy (BBSY):** The BBSY flag can be read to check whether the I<sup>2</sup>C bus (SCL, SDA) is busy or free. In master mode, this bit is also used to issue start and stop conditions.

A high-to-low transition of SDA while SCL is high is recognized as a start condition, setting BBSY to 1. A low-to-high transition of SDA while SCL is high is recognized as a stop condition, clearing BBSY to 0.

To issue a start condition, use a MOV instruction to write 1 in BBSY and 0 in SCP. A retransmit start condition is issued in the same way. To issue a stop condition, use a MOV instruction to write 0 in BBSY and 0 in SCP. It is not possible to write to BBSY in slave mode; the I<sup>2</sup>C bus interface must be set to master transmit mode before issuing a start condition. MST and TRS should both be set to 1 before writing 1 in BBSY and 0 in SCP.

#### Bit 2

| BBSY | Description                        |                 |

|------|------------------------------------|-----------------|

| 0    | Bus is free                        | (Initial value) |

|      | [Clearing condition]               |                 |

|      | When a stop condition is detected  |                 |

| 1    | Bus is busy                        |                 |

|      | [Setting condition]                |                 |

|      | When a start condition is detected |                 |

|      |                                    |                 |

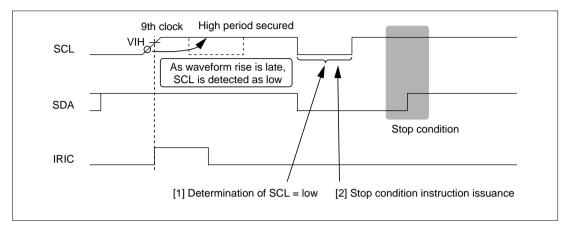

Bit 1—I<sup>2</sup>C Bus Interface Interrupt Request Flag (IRIC): Indicates that the I<sup>2</sup>C bus interface has issued an interrupt request to the CPU. IRIC is set to 1 at the end of a data transfer, when a slave address or general call address is detected in slave receive mode, when bus arbitration is lost in master transmit mode, and when a stop condition is detected. IRIC is set at different times depending on the FS bit in SAR and the WAIT bit in ICMR. See section 16.3.6, IRIC Setting Timing and SCL Control. The conditions under which IRIC is set also differ depending on the setting of the ACKE bit in ICCR.

IRIC is cleared by reading IRIC after it has been set to 1, then writing 0 in IRIC.

When the DTC is used, IRIC is cleared automatically and transfer can be performed continuously without CPU intervention.

| Description                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Waiting for transfer, or transfer in progress (Initial value)                                                                                                                                                                                                             |

| [Clearing conditions]                                                                                                                                                                                                                                                     |

| <ol> <li>When 0 is written in IRIC after reading IRIC = 1</li> <li>When ICDR is written or read by the DTC         (When the TDRE or RDRF flag is cleared to 0)         (This is not always a clearing condition; see the description of DTC operation for</li> </ol>     |

| details) Interrupt requested                                                                                                                                                                                                                                              |

| [Setting conditions]                                                                                                                                                                                                                                                      |

| I <sup>2</sup> C bus format master mode                                                                                                                                                                                                                                   |

| When a start condition is detected in the bus line state after a start condition is issued                                                                                                                                                                                |

| (when the TDRE flag is set to 1 because of first frame transmission)                                                                                                                                                                                                      |

| 2. When a wait is inserted between the data and acknowledge bit when WAIT = 1                                                                                                                                                                                             |

| <ol> <li>At the end of data transfer         <ul> <li>(at the rise of the 9th transmit/receive clock pulse when no wait is inserted,</li> <li>(WAIT=0) and, when a wait is inserted (WAIT=1), at the fall of the 8th transmit/receive clock pulse)</li> </ul> </li> </ol> |

| <ol> <li>When a slave address is received after bus arbitration is lost<br/>(when the AL flag is set to 1)</li> </ol>                                                                                                                                                     |

| 5. When 1 is received as the acknowledge bit when the ACKE bit is 1 (when the ACKB bit is set to 1)                                                                                                                                                                       |

| 12C bus format slave mode  A What the slave address (CVA CVAX) restales.                                                                                                                                                                                                  |

| <ol> <li>When the slave address (SVA, SVAX) matches<br/>(when the AAS and AASX flags are set to 1)</li> </ol>                                                                                                                                                             |

| and at the end of data transfer up to the subsequent retransmission start condition or stop condition detection (when the TDRE or RDRF flag is set to 1)                                                                                                                  |

| 2. When the general call address is detected (when FS = 0 and the ADZ flag is set to 1)                                                                                                                                                                                   |

| and at the end of data transfer up to the subsequent retransmission start condition or stop condition detection (when the TDRE or RDRF flag is set to 1)                                                                                                                  |

| <ol><li>When 1 is received as the acknowledge bit when the ACKE bit is 1<br/>(when the ACKB bit is set to 1)</li></ol>                                                                                                                                                    |

| 4. When a stop condition is detected (when the STOP or ESTP flag is set to 1)  Street received formation and formation made.                                                                                                                                              |

|                                                                                                                                                                                                                                                                           |

- Synchronous serial format, and formatless mode

- 1. At the end of data transfer (when the TDRE or RDRF flag is set to 1)

- 2. When a start condition is detected with serial format selected

- 3. When the SW bit is set to 1 in DDCSWR

Except the above, when the conditions to set the TDRE or RDRF internal flag to 1 is generated

When, with the I<sup>2</sup>C bus format selected, IRIC is set to 1 and an interrupt is generated, other flags must be checked in order to identify the source that set IRIC to 1. Although each source has a corresponding flag, caution is needed at the end of a transfer.

When the TDRE or RDRF internal flag is set, the readable IRTR flag may or may not be set. The IRTR flag (the DTC start request flag) is not set at the end of a data transfer up to detection of a retransmission start condition or stop condition after a slave address (SVA) or general call address match in I<sup>2</sup>C bus format slave mode.

Even when the IRIC flag and IRTR flag are set, the TDRE or RDRF internal flag may not be set. The IRIC and IRTR flags are not cleared at the end of the specified number of transfers in continuous transfer using the DTC. The TDRE or RDRF flag is cleared, however, since the specified number of ICDR reads or writes have been completed.

Table 16.3 shows the relationship between the flags and the transfer states.

**Table 16.3 Flags and Transfer States**

| MST | TRS | BBSY | ESTP | STOP | IRTR | AASX | AL | AAS | ADZ | ACKB | State                                                              |

|-----|-----|------|------|------|------|------|----|-----|-----|------|--------------------------------------------------------------------|

| 1/0 | 1/0 | 0    | 0    | 0    | 0    | 0    | 0  | 0   | 0   | 0    | Idle state (flag clearing required)                                |

| 1   | 1   | 0    | 0    | 0    | 0    | 0    | 0  | 0   | 0   | 0    | Start condition issuance                                           |

| 1   | 1   | 1    | 0    | 0    | 1    | 0    | 0  | 0   | 0   | 0    | Start condition established                                        |

| 1   | 1/0 | 1    | 0    | 0    | 0    | 0    | 0  | 0   | 0   | 0/1  | Master mode wait                                                   |

| 1   | 1/0 | 1    | 0    | 0    | 1    | 0    | 0  | 0   | 0   | 0/1  | Master mode transmit/receive end                                   |

| 0   | 0   | 1    | 0    | 0    | 0    | 1/0  | 1  | 1/0 | 1/0 | 0    | Arbitration lost                                                   |

| 0   | 0   | 1    | 0    | 0    | 0    | 0    | 0  | 1   | 0   | 0    | SAR match by first frame in slave mode                             |

| 0   | 0   | 1    | 0    | 0    | 0    | 0    | 0  | 1   | 1   | 0    | General call address match                                         |

| 0   | 0   | 1    | 0    | 0    | 0    | 1    | 0  | 0   | 0   | 0    | SARX match                                                         |

| 0   | 1/0 | 1    | 0    | 0    | 0    | 0    | 0  | 0   | 0   | 0/1  | Slave mode<br>transmit/receive end<br>(except after SARX<br>match) |

| 0   | 1/0 | 1    | 0    | 0    | 1    | 1    | 0  | 0   | 0   | 0    | Slave mode                                                         |

| 0   | 1   | 1    | 0    | 0    | 0    | 1    | 0  | 0   | 0   | 1    | transmit/receive end (after SARX match)                            |

| 0   | 1/0 | 0    | 1/0  | 1/0  | 0    | 0    | 0  | 0   | 0   | 0/1  | Stop condition detected                                            |

**Bit 0—Start Condition/Stop Condition Prohibit (SCP):** Controls the issuing of start and stop conditions in master mode. To issue a start condition, write 1 in BBSY and 0 in SCP. A retransmit start condition is issued in the same way. To issue a stop condition, write 0 in BBSY and 0 in SCP. This bit is always read as 1. If 1 is written, the data is not stored.

Bit 0

| SCP | Description                                                |                      |

|-----|------------------------------------------------------------|----------------------|

| 0   | Writing 0 issues a start or stop condition, in combination | n with the BBSY flag |

| 1   | Reading always returns a value of 1                        | (Initial value)      |

|     | Writing is ignored                                         |                      |

## 16.2.6 I<sup>2</sup>C Bus Status Register (ICSR)

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0    |

|---------------|--------|--------|--------|--------|--------|--------|--------|------|

|               | ESTP   | STOP   | IRTR   | AASX   | AL     | AAS    | ADZ    | ACKB |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0    |

| Read/Write    | R/(W)* | R/W  |

Note: \* Only 0 can be written, to clear the flags.

ICSR is an 8-bit readable/writable register that performs flag confirmation and acknowledge confirmation and control.

ICSR is initialized to H'00 by a reset and in hardware standby mode.

Bit 7—Error Stop Condition Detection Flag (ESTP): Indicates that a stop condition has been detected during frame transfer in  $I^2C$  bus format slave mode.

#### Bit 7

| ESTP | Description                                             |                 |

|------|---------------------------------------------------------|-----------------|

| 0    | No error stop condition                                 | (Initial value) |

|      | [Clearing conditions]                                   |                 |

|      | 1. When 0 is written in ESTP after reading ESTP = 1     |                 |

|      | 2. When the IRIC flag is cleared to 0                   |                 |

| 1    | In I <sup>2</sup> C bus format slave mode               |                 |

|      | Error stop condition detected                           |                 |

|      | [Setting condition]                                     |                 |

|      | When a stop condition is detected during frame transfer |                 |

|      | In other modes                                          |                 |

|      | No meaning                                              |                 |

**Bit 6—Normal Stop Condition Detection Flag (STOP):** Indicates that a stop condition has been detected after completion of frame transfer in I<sup>2</sup>C bus format slave mode.

Bit 6

| STOP | Description                                                          |

|------|----------------------------------------------------------------------|

| 0    | No normal stop condition (Initial value)                             |

|      | [Clearing conditions]                                                |

|      | 1. When 0 is written in STOP after reading STOP = 1                  |

|      | 2. When the IRIC flag is cleared to 0                                |

| 1    | In I <sup>2</sup> C bus format slave mode                            |

|      | Normal stop condition detected                                       |

|      | [Setting condition]                                                  |

|      | When a stop condition is detected after completion of frame transfer |

|      | In other modes                                                       |

|      | No meaning                                                           |

# Bit 5—I<sup>2</sup>C Bus Interface Continuous Transmission/Reception Interrupt Request Flag

(**IRTR**): Indicates that the I<sup>2</sup>C bus interface has issued an interrupt request to the CPU, and the source is completion of reception/transmission of one frame in continuous transmission/reception for which DTC activation is possible. When the IRTR flag is set to 1, the IRIC flag is also set to 1 at the same time.

IRTR flag setting is performed when the TDRE or RDRF flag is set to 1. IRTR is cleared by reading IRTR after it has been set to 1, then writing 0 in IRTR. IRTR is also cleared automatically when the IRIC flag is cleared to 0.

| Bit 5 |                                                                |                 |

|-------|----------------------------------------------------------------|-----------------|

| IRTR  | Description                                                    |                 |

| 0     | Waiting for transfer, or transfer in progress                  | (Initial value) |

|       | [Clearing conditions]                                          |                 |

|       | 1. When 0 is written in IRTR after reading IRTR = 1            |                 |

|       | 2. When the IRIC flag is cleared to 0                          |                 |

| 1     | Continuous transfer state                                      |                 |

|       | [Setting condition]                                            |                 |

|       | <ul> <li>In I<sup>2</sup>C bus interface slave mode</li> </ul> |                 |

|       | When the TDRE or RDRF flag is set to 1 when AASX = 1           |                 |

|       | <ul> <li>In other modes</li> </ul>                             |                 |

**Bit 4—Second Slave Address Recognition Flag (AASX):** In I<sup>2</sup>C bus format slave receive mode, this flag is set to 1 if the first frame following a start condition matches bits SVAX6 to SVAX0 in SARX.

When the TDRE or RDRF flag is set to 1

AASX is cleared by reading AASX after it has been set to 1, then writing 0 in AASX. AASX is also cleared automatically when a start condition is detected.

Bit 4

| AASX | Description                                                          |                 |

|------|----------------------------------------------------------------------|-----------------|

| 0    | Second slave address not recognized                                  | (Initial value) |

|      | [Clearing conditions]                                                |                 |

|      | 1. When 0 is written in AASX after reading AASX = 1                  |                 |

|      | 2. When a start condition is detected                                |                 |

|      | 3. In master mode                                                    |                 |

| 1    | Second slave address recognized                                      |                 |

|      | [Setting condition]                                                  |                 |

|      | When the second slave address is detected in slave receive mode whil | e FSX = 0       |

**Bit 3—Arbitration Lost (AL):** This flag indicates that arbitration was lost in master mode. The I<sup>2</sup>C bus interface monitors the bus. When two or more master devices attempt to seize the bus at nearly the same time, if the I<sup>2</sup>C bus interface detects data differing from the data it sent, it sets AL to 1 to indicate that the bus has been taken by another master.

AL is cleared by reading AL after it has been set to 1, then writing 0 in AL. In addition, AL is reset automatically by write access to ICDR in transmit mode, or read access to ICDR in receive mode.

#### Bit 3

| AL | Description                                                                              |                    |  |  |

|----|------------------------------------------------------------------------------------------|--------------------|--|--|

| 0  | Bus arbitration won                                                                      | (Initial value)    |  |  |

|    | [Clearing conditions]                                                                    |                    |  |  |

|    | 1. When ICDR data is written (transmit mode) or read (receive                            | e mode)            |  |  |

|    | 2. When 0 is written in AL after reading AL = 1                                          |                    |  |  |

| 1  | Arbitration lost                                                                         |                    |  |  |

|    | [Setting conditions]                                                                     |                    |  |  |

|    | <ol> <li>If the internal SDA and SDA pin disagree at the rise of SCL<br/>mode</li> </ol> | in master transmit |  |  |

|    | 2. If the internal SCL line is high at the fall of SCL in master tra                     | ansmit mode        |  |  |

**Bit 2—Slave Address Recognition Flag (AAS):** In I<sup>2</sup>C bus format slave receive mode, this flag is set to 1 if the first frame following a start condition matches bits SVA6 to SVA0 in SAR, or if the general call address (H'00) is detected.

AAS is cleared by reading AAS after it has been set to 1, then writing 0 in AAS. In addition, AAS is reset automatically by write access to ICDR in transmit mode, or read access to ICDR in receive mode.

Bit 2

| AAS | Description                                                                  |                    |  |  |

|-----|------------------------------------------------------------------------------|--------------------|--|--|

| 0   | Slave address or general call address not recognized                         | (Initial value)    |  |  |

|     | [Clearing conditions]                                                        |                    |  |  |

|     | 1. When ICDR data is written (transmit mode) or read (receive                | e mode)            |  |  |

|     | 2. When 0 is written in AAS after reading AAS = 1                            |                    |  |  |

|     | 3. In master mode                                                            |                    |  |  |

| 1   | Slave address or general call address recognized                             |                    |  |  |

|     | [Setting condition]                                                          |                    |  |  |

|     | When the slave address or general call address is detected in while $FS = 0$ | slave receive mode |  |  |

Bit 1—General Call Address Recognition Flag (ADZ): In I<sup>2</sup>C bus format slave receive mode, this flag is set to 1 if the first frame following a start condition is the general call address (H'00).

ADZ is cleared by reading ADZ after it has been set to 1, then writing 0 in ADZ. In addition, ADZ is reset automatically by write access to ICDR in transmit mode, or read access to ICDR in receive mode.

Bit 1

| ADZ | Description                                                                                 |                 |

|-----|---------------------------------------------------------------------------------------------|-----------------|

| 0   | General call address not recognized                                                         | (Initial value) |

|     | [Clearing conditions]                                                                       |                 |

|     | 1. When ICDR data is written (transmit mode) or read (receive r                             | mode)           |

|     | 2. When 0 is written in ADZ after reading ADZ = 1                                           |                 |

|     | 3. In master mode                                                                           |                 |

| 1   | General call address recognized                                                             |                 |

|     | [Setting condition]                                                                         |                 |

|     | When the general call address is detected in slave receive mode while $FSX = 0$ or $FS = 0$ | •               |

**Bit 0—Acknowledge Bit (ACKB):** Stores acknowledge data. In transmit mode, after the receiving device receives data, it returns acknowledge data, and this data is loaded into ACKB. In receive mode, after data has been received, the acknowledge data set in this bit is sent to the transmitting device.

When this bit is read, in transmission (when TRS = 1), the value loaded from the bus line (returned by the receiving device) is read. In reception (when TRS = 0), the value set by internal software is read.

When this bit is written to, the acknowledge data transmitted at the receipt is rewritten regardless of the TRS value. The data loaded from the receiving device is retained, therefore take care of using bit-manipulation instructions.

Bit 0

| ACKB | Description                                                                                    |    |

|------|------------------------------------------------------------------------------------------------|----|

| 0    | Receive mode: 0 is output at acknowledge output timing (Initial value)                         |    |

|      | Transmit mode: Indicates that the receiving device has acknowledged the data (sign is 0)       | al |

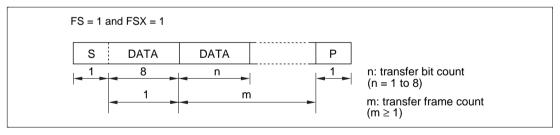

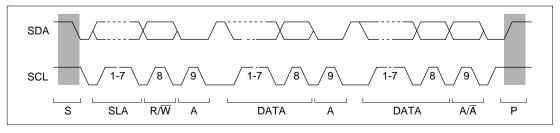

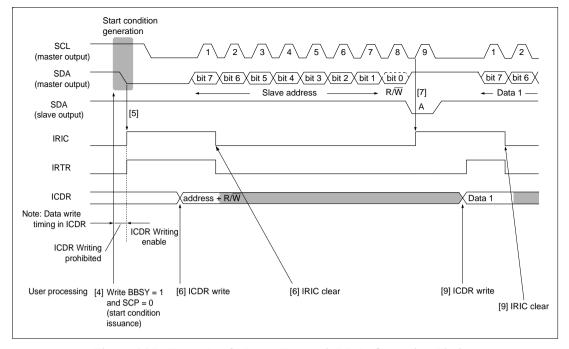

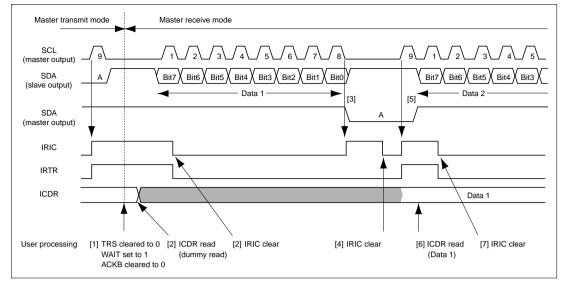

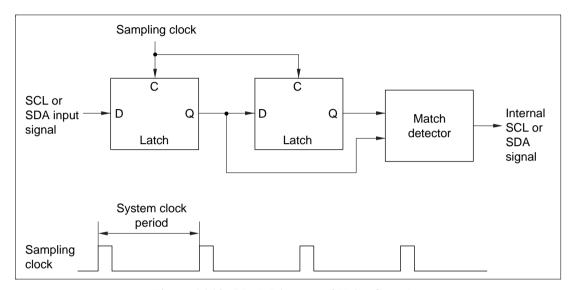

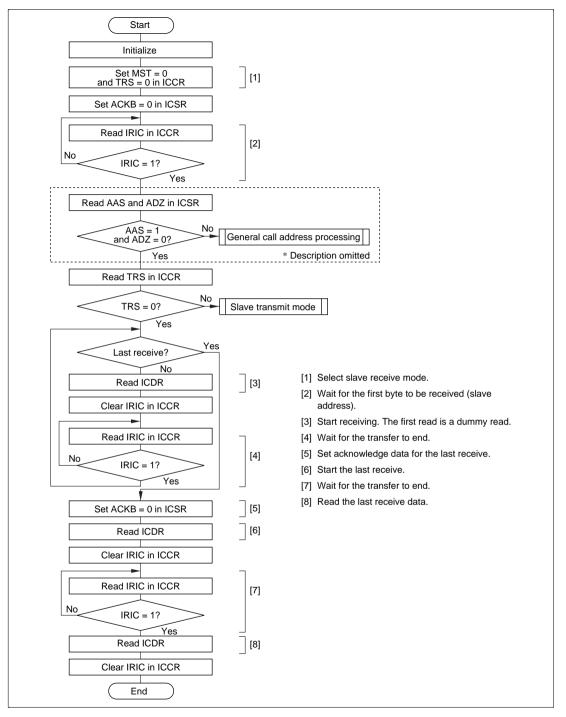

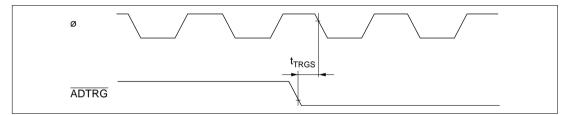

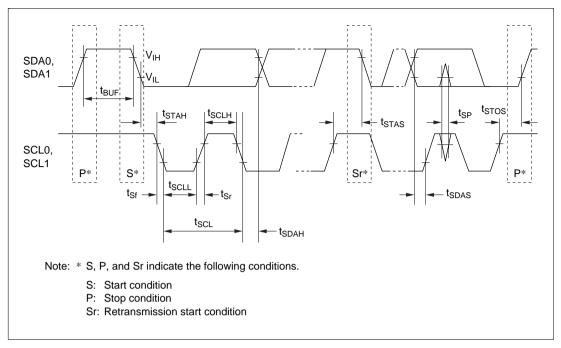

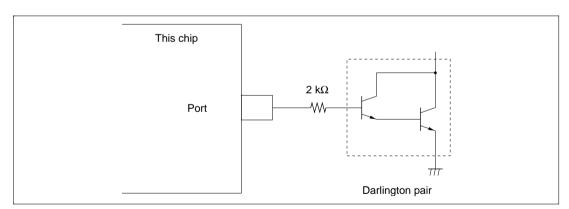

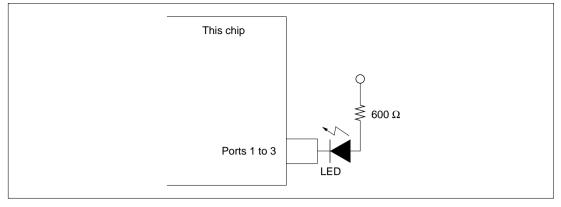

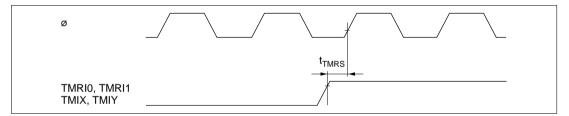

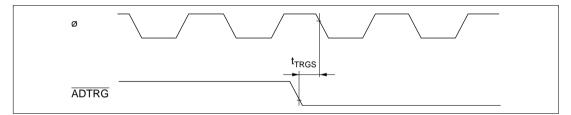

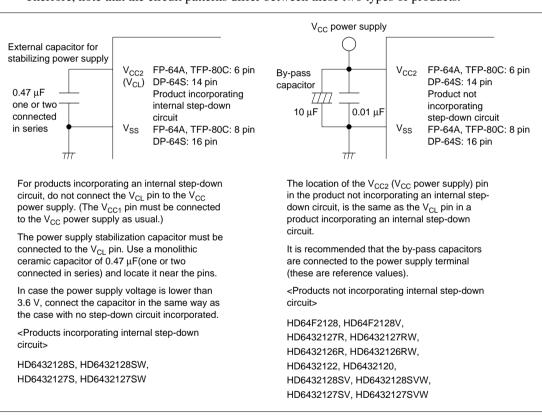

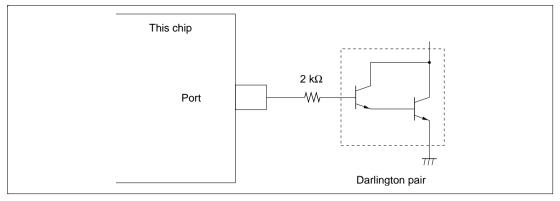

| 1    | Receive mode: 1 is output at acknowledge output timing                                         |    |